航姿信号模拟器是为了给待测的仪表设备或实验室研究提供可以人工调节和控制的信号源而设计的,可以产生各种频率的航姿信号及用户自己定义的任意波形等,以便对飞机性能进行测试。传统的航姿信号模拟系统开发是基于VXI、PCI等总线基础上,大多使用硬件电路设计与实现,通过PC机进行分析处理,功能相对来说也比较完善,但是电路的结构比较复杂,体积过于庞大,不适合在外场使用,并且传统的模拟器使用范围比较局限,就造成了在成本方面有许多的浪费,因此开发一个新型的、可编程的通用型模拟器是非常有必要的。本文设计的是一种便携式的航姿信号模拟器,不但体积小携带方便,而且处理器采用的是具有高速数据计算能力的DSP。可以对旋转变压器输出的轴角信号进行预处理、传输、显示及存储等。该系统可以广泛用于航空、航天、雷达和火炮控制等军用装备,也可以用于数控机床和机器人等民用设备中,应用前景广阔。

电源设计

DSP芯片由于采用两种不同的电压,内核1.8 V电压和IO口3.3 V电压,所以对DSP系统供电时一般都采取双电源,本设计方案中采用TI公司专门为DSP配套的电源芯片TPS767 D301来提供电源,这款芯片属于线性DC/DC变换芯片,给TPS767D301提供5 V的直流电源就可以产生满足F2812的3.3 V和1.8 V的电压,直接给DSP提供电源,此外这个电源芯片的最大输出电流可以达到1 A,可以同时给DSP芯片和少量的外围电路供电。

时钟和复位电路

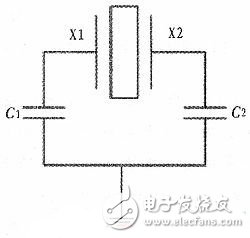

DSP2812芯片的时钟有两种引脚连接方式,一种是利用其内部所提供的晶振电路,在其X1/XCLKIN和X2引脚之间连接一晶体来启动内部振荡器;另一种是直接将外部的时钟源直接输入X1/XCLKIN引脚上,X2引脚悬空,本设计中采用的为第一种方法,如图3所示。

DSP2812芯片具有锁相环时钟模块(PLL),可以输入时钟进行倍频,所以采用30 MHz的外接晶振,经过锁相环倍频后,能够实现系统的150 MHz要求。由于电源模块TPS767D301芯片自身能够产生复位信号,且此复位信号可以直接供DSP芯片使用,所以本设计中没有设置专门的复位芯片。

转换芯片工作原理及其与DSP接口设计

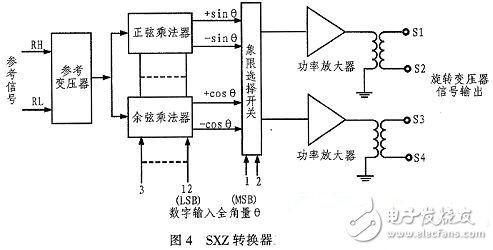

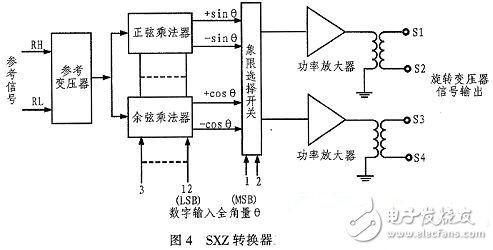

12SXZ转换芯片由以下几部分组成:参考变压器、象限选择开关、正余弦乘法器、功率放大器、输出变压器等五部分。数字全角量和参考信号输入经正、余弦乘法器之后,被转换成代表角度的正余弦信号,再经功率放大器放大后,具有了1.3VA的负载能力,再经输出变压器隔离、升压后,变成自整角机/旋转变压器形式的三线、四线模拟信号输出。

其中等式左边为输出电压,θ为输入数字角,K为比例系数,URH-RL是参考电压。转换器的工作原理框图如图4所示。

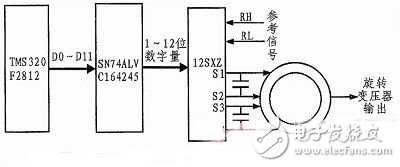

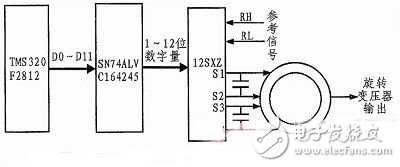

模拟器的核心是DSP 2812,通过软件控制能产生所需要的航姿信号,并且系统带有自检功能,在系统设计中,DSP控制I/O口直接对12SXZ进行操作,产生模拟信号。上面我们知道DSP有两种电压,I/O口的电压为3.3 V,我们所用到的转换芯片为TTL电平5 V电压,考虑到DSP产生信号的驱动能力,首先需要电平转换,把DSP端口输出的3.3 V电平转变为5 V。采用的电平转换芯片为SN74ALVC164245,此芯片是16路双向的电平转换芯片,由引脚DIR控制其转换方向。转换芯片SXZ为12位数度的转换器,用DSP的数据口D0~D11与电平转换芯片中的12路相连,转换后的12位电平再与SXZ的12位数字量输入端相连,DSP与12SXZ转换器接口电路如图5所示。

文中介绍了基于DSP技术的航姿信号模拟器的硬件设计电路,该方法克服了传统模拟技术的结构复杂、精度低、可靠性差等缺点。通过软件编程能够实现航向姿态信号,通过对本模拟器的开发、调试到应用,使得模拟器具有低功耗低、体积小等优点,便于现场调试,可以在多种环境下使用,能够在排除飞机故障及维护飞机安全及提高飞行质量等方面会有重大改善。

设计选用的核心控制芯片是TMS320F2812,但是必须提供基本的外围电路才能发挥核心控制电路的作用。一个典型的DSP最小系统应该包括 DSP芯片、还有为DSP芯片提供合适电源的电源电路、触发DSP初始化的复位电路、时钟电路及用于在线仿真和下载的JTAG接口电路。另外由于考虑到需 要跟上位机进行通信,完成数据和控制信号的传送,在此基础上添加了串口通信电路。DSP的基本系统框图如图2所示,外扩RAM是用来放置大量的信号数据, 而外扩FLASH是用来存放控制程序。

本文提出一种基于FPGA 的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。用QuartusⅡ软件在FPGA 平台上完成了数字核脉冲的幅度提取并生成能谱。在此基础上通过电路设计建立了数字化能谱测量实验装置,实测了137Cs的能谱,测量结果与相同条件下的模拟能谱仪的实测谱完全吻合。由此证明基于FPGA 的数字多道脉冲幅度分析器硬件设计方案的正确可行,具有实用性。

多道脉冲幅度分析仪和射线能谱仪是核监测与和技术应用中常用的仪器。20世纪90年代国外就已经推出了基于高速核脉冲波形采样和数字滤波成型技术的新型多道能谱仪,使数字化成为脉冲能谱仪发展的重要方向。国内谱仪技术多年来一直停留在模拟技术水平上,数字化能谱测量技术仍处于方法研究阶段。为了满足不断增长的高性能能谱仪需求,迫切需要研制一种数字化γ能谱仪。通过核脉冲分析仪显示在显示器上的核能谱帮助人们了解核物质的放射性的程度。

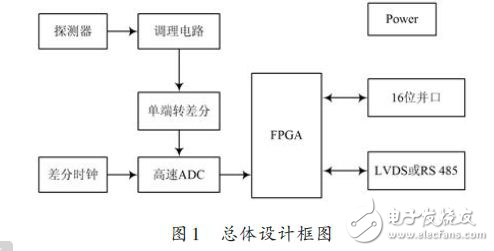

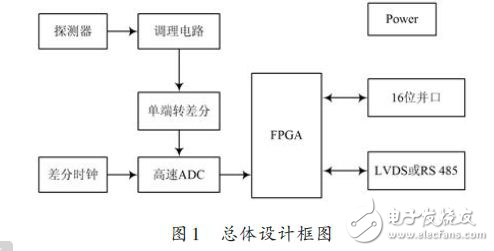

图1即为总体设计框图,探测器输出的核脉冲信号经前端电路简单调理后,经单端转差分,由采样率为65 MHz 的高速ADC 在FPGA 的控制下进行模/数转换,完成核脉冲的数字化,并通过数字核脉冲处理算法在FPGA 内形成核能谱,核能谱数据可通过16 位并行接口传输至其他谱数据处理终端, 也可通过LVDS/RS 485接口实现远程传输。特别需要注意的是,由于高速AD 前置,调理电路应该满足宽带、高速,且电路参数能够动态调整的需要,以适应不同类型探测器输出的信号,从而更好地发挥数字化技术的优势。

前端电路

前端电路由单端转差分和高速ADC 电路组成。差分电路由于其良好的抗共模干扰能力而应用广泛。由于调理电路输出的脉冲信号为单极性信号,若直接送入ADC,将损失一半的动态范围。设计中在运放中加入一个适当的偏置电压,将单极性信号转换成双极性信号后再送入ADC,以保证动态范围。将信号由单端转换成差分的同时,进行抗混叠滤波处理,完成带宽的调整。

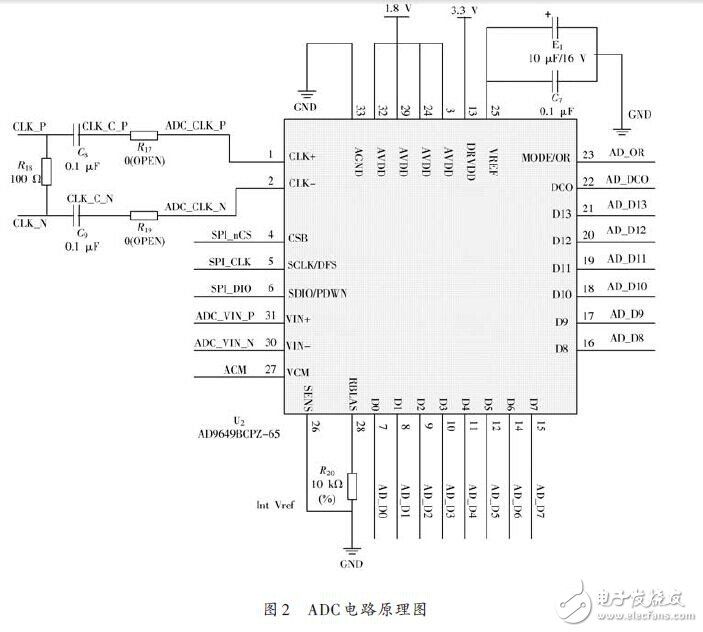

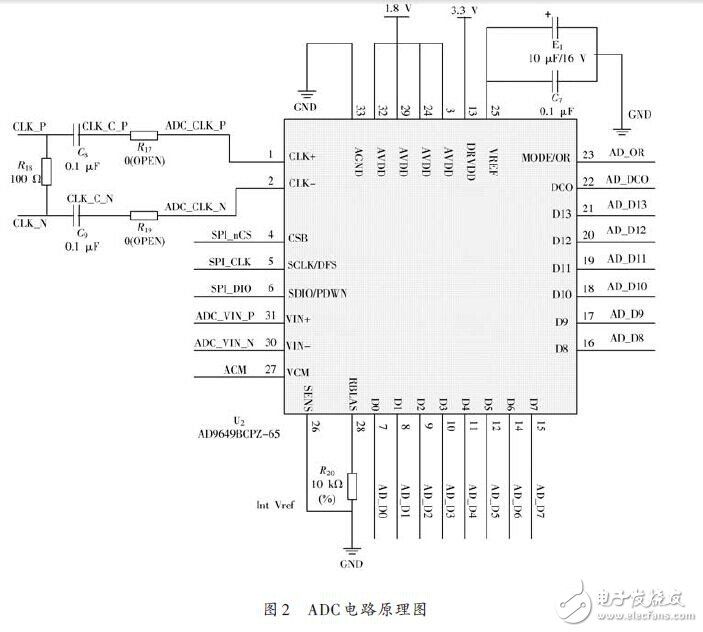

本设计使用AD9649 - 65 高速ADC 实现核脉冲的模/数转换,AD9649为14 位并行输出的高速模/数转换器,具有功耗低、尺寸小、动态特性好等优点。当信号从探测器通过调理电路,过差分转单端电路后,以差分信号的形式进入ADC, 在差分时钟的控制下,转换成14 位数据,进入FPGA.该高速A/D 在外部FPGA 的控制下对信号进行采样。然后将采样后的数字信号送入FPGA 中实现数字核脉冲的幅度提取。图2 为A/D 转换的原理图,AD9649在差分时钟的同步下完成A/D 转换,D0~D13为14个有效输出数据位。

FPGA

目前国内外多道脉冲幅度分析的数字化实现主要有2种方案:纯DSP 方案、DSP+可编程器件方案。本文将充分发挥FPGA 的并行处理优势,在单片FPGA芯片上实现核脉冲的采集与数字核脉冲处理算法,经Quar-tus-Ⅱ软件仿真与综合,本文选用EP3C40 FPGA 芯片实现多道分析器的数字化功能。

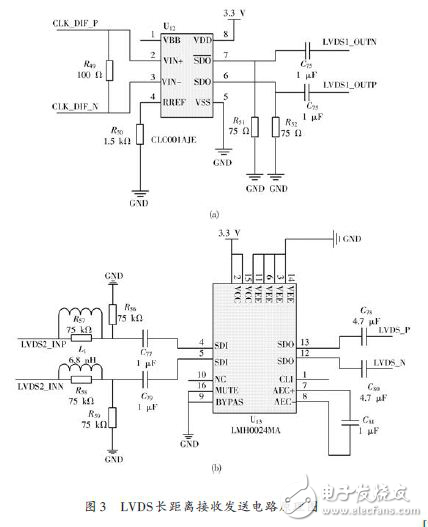

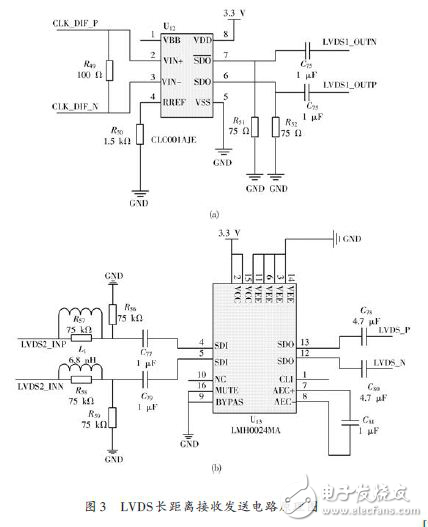

接口电路设计采用了LVDS 和RS485两种长距离数据传输接口,用于实现核能谱数据的远程传输。LVDS 即低电压差分信号,是一种可以实现点对点或一点对多点的连接,具有低功耗,低误码率,低串扰,低噪声和低辐射等特点。LVDS 在对信号完整性、地抖动及共模特性要求较高的系统中得到了越来越广泛的应用。图3为低电压、最高数据传输速率为655 Mb/s 的LVDS 接口电路。

基于FPGA 的数字核脉冲分析器硬件设计方案。该方案在单片FPGA 中实现了多道脉冲幅度的数字分析功能,通过软件功能仿真和实际运行,说明了数字多道脉冲幅度分析器硬件设计的可行性,将FPGA 应用到数字能谱测量系统能充分发挥其并行处理优势,并能有效降低硬件电路设计的复杂度。