8085是8位可编程微处理器芯片,由INTEL于1977年首次设计,使用NMOS晶体管。

8085微处理器的特点

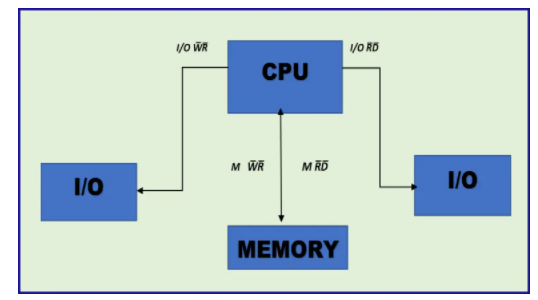

8085微处理器的BUS架构

各种I / O设备和存储设备通过一组线路或电线连接到CPU,这些线路或电线称为BUS。总线分为三类:

1、地址总线

当地址由CPU发送时,所有设备都通过地址BUS连接到CPU并接收该地址,但是只有设备会响应,该设备还会从CPU接收芯片使能信号。 地址BUS是 单向。

2、数据总线

它通过存储单元或外围部件(内存或I / O写入/存储器或I / O读取)承载来自微处理器的数据值。 数据总线为双向。 因此,信息在8085微处理器与内存或I / O设备之间双向流动。

3、控制总线

它在中央处理器,存储器输入/输出设备之间传送控制信号。 也是双向。

8085微处理器的BUS架构

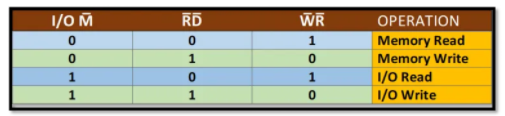

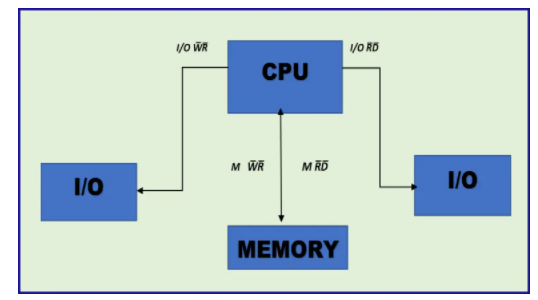

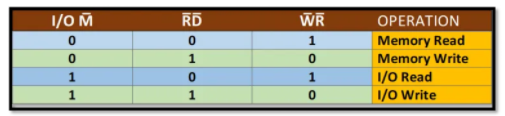

I / OM? – 当信号为高电平(逻辑1)时,CPU希望与I / O设备通信;但是当信号为低电平(逻辑o)时,CPU将与内存通信。

R?D?– 当CPU发送低R?D?信号时,被激活的设备知道CPU要从另一设备或存储器中读取信息。

W?R?T?– 当CPU发送低W?R?T?信号时,被激活的设备知道CPU要向内存或其他设备写入信息。

8085微处理器中包含三个分类区域

1、ALU:

这部分执行减法,逻辑或的加法,补语,右移,左移等操作。

2、寄存器:

寄存器用于临时存储数据插入; 它有以下寄存器,

8 BIT 累加器

8 BIT 通用寄存器(BC,DE,HL)

一个16位 堆栈指针

一个16位 程序计数器

指令 Reg

3、时序与控制:

这些主要负责时间和控制信号的产生,这对于完成指令操作至关重要。 它可以控制CPU与外围设备之间的数据流,并为存储器和I / O设备的操作提供定时信号。

说明示例:

1字节指令– MOV B,C

2字节指令– MVI B,05

3字节指令– 左手5000H

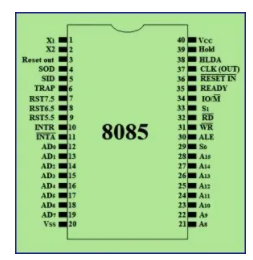

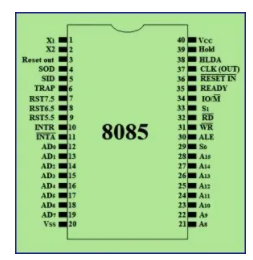

8085微处理器的PIN图

8085微处理器的PIN图

8085微处理器的引脚说明

A8 - A15:

这些地址总线曾经是8位I / O设备存储器地址的最高有效位。

AD0 - AD7:

当地址与数据复用时,则称为AD 总线。 低位或低位有效总线以及数据总线用于存储器地址或I / O地址。

ALE:

ALE引脚在第一个周期被激活,并使地址数据总线的低8位被锁存(逻辑0);当ALE为逻辑1时,地址总线被激活。

I / OM?:

这是用于存储为I / O设备的状态信号。 当信号变高时,它将对所有I / O设备起作用。 当信号变低时,它将用于存储。

R?D?:

这是一个控制读取操作的信号; 当信号为低电平时,它将从I / O设备或O / P设备读取数据。

W?R?T?:

它是指定的写控制信号。 该信号指定数据总线上的数据将被写入指定的存储器或I / O设备。

READY:

高电平有效的I / P控制信号。 μP使用它来识别外设是否完成了数据传输。

HLDA:这是用于批准保持请求的保持确认信号。

TRAP: 它在所有中断中具有最高优先级。 如果出现任何紧急情况,它将正常工作。

RST 7.5: TRAP之后的下一个优先级是RST 7.5

RST 6.5: RST 7.5之后的下一个优先级是RST 6.5

RST 5.5: RST 6.5之后的下一个优先级是RST 5.5

INTR R:

这是一个用作通用中断的中断请求。 优先级最低。

I?N?T?A?:

该信号为中断确认。 用于确认所有中断。

RESET IN:

如果该引脚上的信号变为低电平,则设备程序计数器将被设置为零,并且当它递增时,它将处于复位状态。

RESET OUT:

该信号表示up被复位,并被用作复位存储设备和输入输出设备。

SID:

串行I / P数据是信号i / p的数据线,该数据线已加载到累加器的第7位。

SOD:

串行o / p数据是累加器的第7位,即SOD线上的o / p。

X1 - X2 [时钟输入]:

这两个输入作为时钟输入执行。

时钟O / P:

进程运行的频率相同。

VCC &GND:

VCC 连接到+ 5V; GND引脚接地。